DECISION 17 rue de l'Amiral Hamelin 75116 PARIS – France phone: + 33 1 45 05 70 13 fax: + 33 1 45 05 72 65

www.decision.eu

FUTURE HORIZONS 44 Bethel Road Sevenoaks, Kent TN13 3UE – England phone: +44 (0)1732 740440 fax: +44 (0)1732 740442

www.futurehorizons.com

# SMART 2010/062:

Benefits and Measures to Set Up 450mm Semiconductor Prototyping and to Keep Semiconductor Manufacturing in Europe

- The role of Public Authorities and Programmes -

# **Final Report**

The opinions expressed here are those held by the study team at the time of publication of this Report and do not necessarily represent the Commission's official position.

Date: 16<sup>th</sup> February 2012

(This Page Intentionally Left Blank)

# **Table Of Contents**

| 1.                                                                                                          | Executive Summary                                                                                                                                                                                                                                                                      | 9                                                        |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2.                                                                                                          | Overview                                                                                                                                                                                                                                                                               | 13                                                       |

| 3.                                                                                                          | Introduction                                                                                                                                                                                                                                                                           | 17                                                       |

| <b>4.</b><br>4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.<br>4.7.                                           | State-Of-The-Art SC Manufacturing In Europe<br>Introduction<br>IC Manufacturing In Europe<br>European Companies Manufacturing Elsewhere<br>The 'Fab-Lite' Alternative<br>European Market Position<br>Other European Manufacturing Strengths<br>Semiconductor Manufacturing Conclusions | 19<br>20<br>21<br>21<br>24<br>25                         |

| <b>5.</b><br>5.1.<br>5.2.<br>5.3.<br>5.3.2.<br>5.3.3.<br>5.4.<br>5.5.<br>5.5.1.<br>5.5.2.<br>5.5.3.<br>5.6. | The 450mm Bifurcation                                                                                                                                                                                                                                                                  | 29<br>29<br>31<br>32<br>32<br>32<br>34<br>34<br>35<br>36 |

| <b>6.</b><br>6.1.<br>6.2.<br>6.3.<br>6.3.1.<br>6.3.2.<br>6.3.3.<br>6.4.<br>6.5.<br>6.6.<br>6.7.             | Semiconductor Technology & Processes                                                                                                                                                                                                                                                   | 39<br>40<br>41<br>43<br>44<br>45<br>46<br>47             |

| <b>7.</b><br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.                                           | 450mm Fab Sizing & Loading Models                                                                                                                                                                                                                                                      | 49<br>50<br>51<br>52<br>53<br>53                         |

| <b>8.</b><br>8.1.                                                                                           | Industry Impact Of 450mm Processing<br>Effect Of 450mm On Existing 300mm & 200mm Manufacturing Infrastructures                                                                                                                                                                         |                                                          |

| 8.2.<br>8.3.                                                                                                                                                                                                        | Upgrade Of Existing 300mm Fabs & Tools<br>Summary & Conclusions                                                                                                                                                                                                                                 |                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| <ol> <li>9.1.</li> <li>9.2.</li> <li>9.3.</li> <li>9.4.</li> <li>9.5.</li> <li>9.6.</li> <li>9.7.</li> <li>9.8.</li> <li>9.9.</li> <li>9.10.</li> <li>9.11.</li> <li>9.12.</li> <li>9.13.</li> <li>9.14.</li> </ol> | Impact On Equipment & Materials Technologies<br>Lithography.<br>Deposition<br>CMP<br>Wafer Handling.<br>Metrology.<br>Cross-Fertilisation With PV & LCD Processing.<br>Wafer Production.<br>Gases.<br>Dopants.<br>Low-k Materials<br>Slurries.<br>Masks.<br>Security Of Supply.<br>Conclusions. | .61<br>.62<br>.62<br>.62<br>.62<br>.62<br>.62<br>.63<br>.64<br>.64<br>.64<br>.65<br>.65 |

| <b>10.</b><br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.<br>10.6.<br>10.7.                                                                                                                                           | 450mm Cost Analysis<br>Increased Wafer Area<br>Substrate Costs<br>Wafer Processing Material Usage Costs<br>Wafer Processing Energy Usage Costs<br>Wafer Processing Costs<br>Wafer Handling Costs<br>Total Cost Per Finished Die                                                                 | .67<br>.68<br>.68<br>.68<br>.69<br>.69                                                  |

| <b>11.</b><br>11.1.<br>11.2.                                                                                                                                                                                        | Semiconductor Supply Chain Upstream Links<br>Material & Equipment Suppliers<br>Research & Development                                                                                                                                                                                           | .71                                                                                     |

| <b>12.</b><br>12.1.<br>12.2.<br>12.3.                                                                                                                                                                               | Downstream Links With End Systems & Services<br>Semiconductors Are An Enabling Industry<br>Competitiveness Of Integrating Industries<br>Manufacturing Crucial For Strategic Independence                                                                                                        | .73<br>.74                                                                              |

| <b>13.</b><br>13.1.<br>13.2.<br>13.3.<br>13.4.                                                                                                                                                                      | Economic Impact Of Advanced IC Manufacturing<br>Impact On Trade Balance<br>Impact On Employment<br>Return On Public Investment<br>Summary & Conclusions                                                                                                                                         | .81<br>.82                                                                              |

| <b>14.</b><br>14.1.<br>14.2.<br>14.3.                                                                                                                                                                               | Public Support For Semiconductor Manufacturing<br>Introduction<br>Worldwide Public Subsidies of Wafer Fabs<br>Technical Education                                                                                                                                                               | .87<br>.88                                                                              |

| <b>15.</b><br>15.1.<br>15.2.<br>15.3.<br>15.4.                                                                                                                                                                      | Impact of R&D Funding<br>Semiconductor Industry R&D Funding Rationale<br>Competitive Landscape<br>Current Status In Europe<br>Current Outlook In Europe                                                                                                                                         | .93<br>.93<br>.96                                                                       |

| 16.     | EU SC Industry Position On 450mm                            | .99 |

|---------|-------------------------------------------------------------|-----|

| 16.1.   | 450mm Semiconductor R&D In Europe                           | 99  |

| 16.1.1. | European R&D Strengths                                      | 100 |

| 16.1.2. | European R&D Weaknesses                                     | 101 |

| 16.1.3. | European R&D Threats                                        | 101 |

|         | Other R&D Issues                                            |     |

| 16.2.   | Current 450mm Dilemma In Europe                             | 102 |

| 16.2.1. | Industry Positions                                          | 102 |

| 16.2.2. | National PA Positions                                       |     |

| 16.3.   | Return On Investment                                        | 103 |

| 16.4.   | Summary & Conclusions                                       | 105 |

| 17.     | Scenarios & Impact Assessment                               | 107 |

| 17.1.   | •                                                           |     |

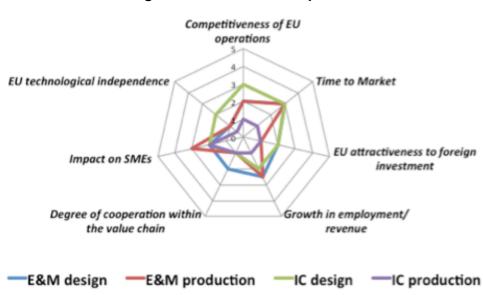

| 17.1.1. | Scenario 1 Description                                      |     |

|         | Impact Assessment                                           |     |

|         | Cost                                                        |     |

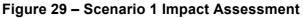

| 17.2.   | Scenario 2: 450 Support Programme To E&M Suppliers          | 111 |

|         | Scenario 2 Description                                      |     |

|         | Impact Assessment                                           |     |

|         | Cost & Feasibility                                          |     |

| 17.3.   | Scenario 3: Support To 450mm Device Manufacturing In Europe | 117 |

|         | Scenario 3 Description                                      |     |

| 17.3.2. | Impact Assessment                                           | 119 |

| 17.3.3. | Cost                                                        | 123 |

| 17.4.   | Cumulated Impact Of Scenarios                               | 124 |

| 17.5.   | Conclusions On Scenarios                                    | 126 |

# List Of Figures

| Figure 1 – Project Task Flow                                                             | 14   |

|------------------------------------------------------------------------------------------|------|

| Figure 2 – Project Interviews                                                            | . 15 |

| Figure 3 – Simplified Wafer Fabrication Process                                          | 19   |

| Figure 4 – Current & Potential 450mm Adopters                                            | 33   |

| Figure 5 – Best Case 450mm Rollout Timing                                                | 36   |

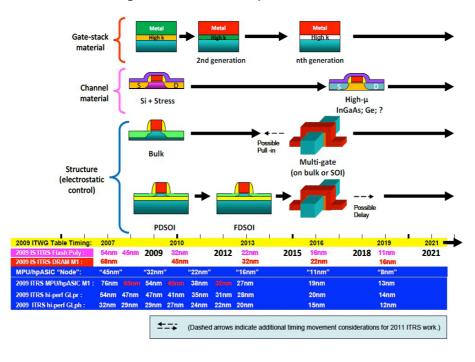

| Figure 6 – ORTC Graph Of Trends                                                          | 43   |

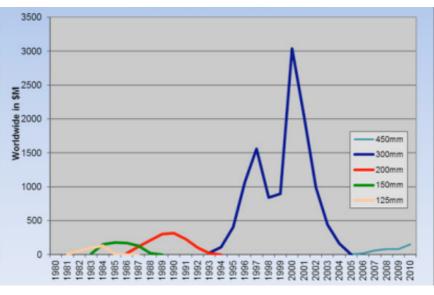

| Figure 7 – Equipment Industry Spending To Develop New Wafer Size Platforms               | . 55 |

| Figure 8 – Possible Cross-Fertilization Areas From 450mm To 300mm                        | . 58 |

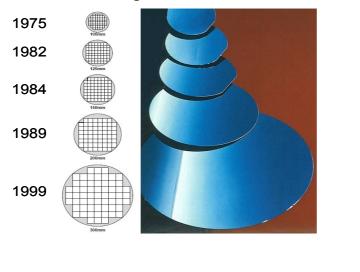

| Figure 9 – Previous Wafer Size Transitions                                               | 67   |

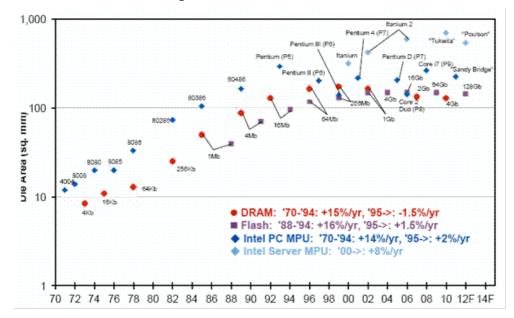

| Figure 10 – Die Size Trends                                                              | 68   |

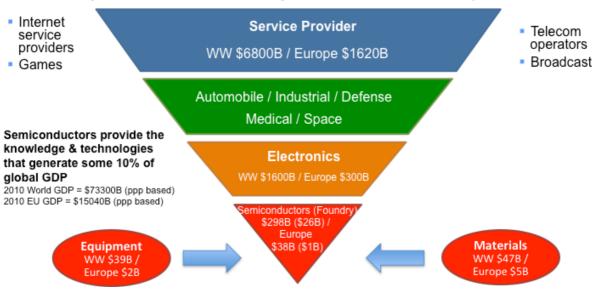

| Figure 11 – Economic Leverage Of Semiconductor Supply Chain                              | 73   |

| Figure 12 – European Electronic Equipment Production                                     | 75   |

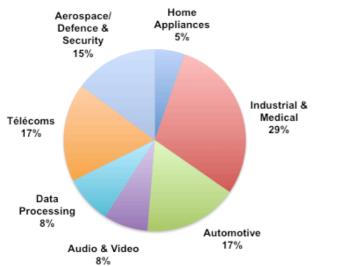

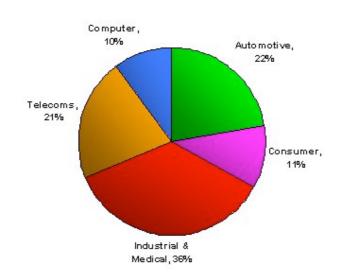

| Figure 13 – European Semiconductor Sales By Application                                  | 76   |

| Figure 14 – Application Segment By Semiconductor Technology                              | 77   |

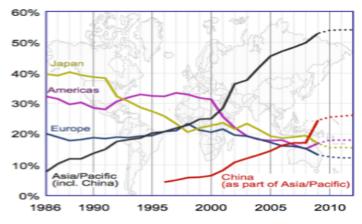

| Figure 15 – Semiconductor Sales By Region, 1986-2010                                     | 79   |

| Figure 16 – Regional Share Of Semiconductor Sales, 2008 & 2010                           | . 80 |

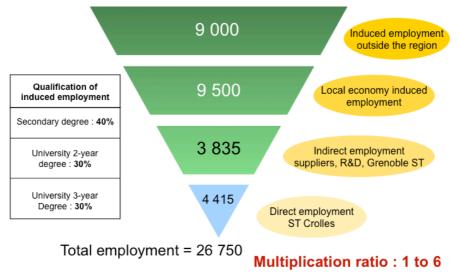

| Figure 17 – Impact Of Employment, Crolles Case Study                                     | 82   |

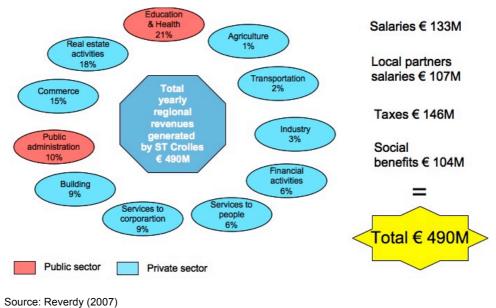

| Figure 18 – Semiconductor Activity Regional Revenue Distribution                         | 83   |

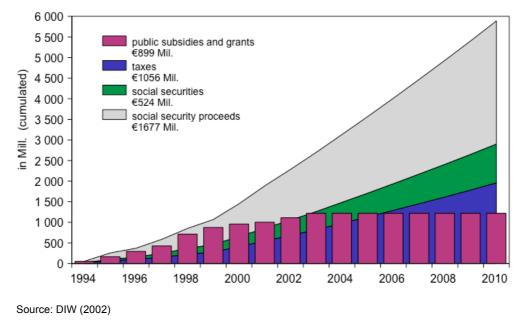

| Figure 19 – Public Subsidies Fiscal Effects Of AMD & Infineon Investments (excl Fab 36). | 84   |

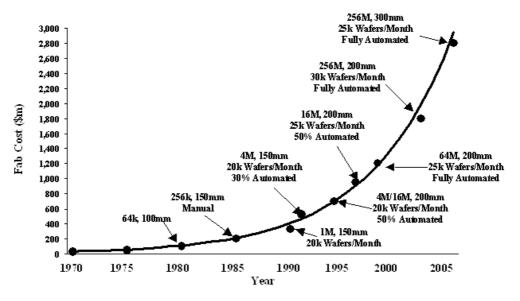

| Figure 20 – Semiconductor Wafer Fab Cost Trends                                          | 87   |

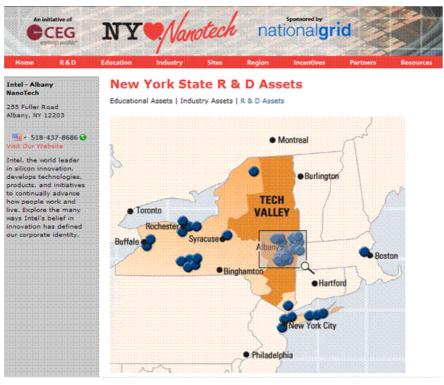

| Figure 21 – NY State Technology Cluster                                                  | 94   |

| Figure 22 – Albany Cluster Partners                                                      | 94   |

| Figure 23 – Annual Public Funding To ENIAC Joint Technology Initiative (JTI)             | 96   |

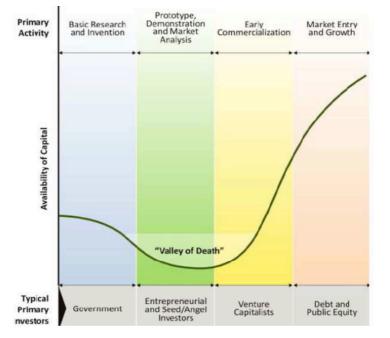

| Figure 24 – Funding "Valley Of Death"                                                    | 97   |

| Figure 25 – European R&D SWOT                                                            | 99   |

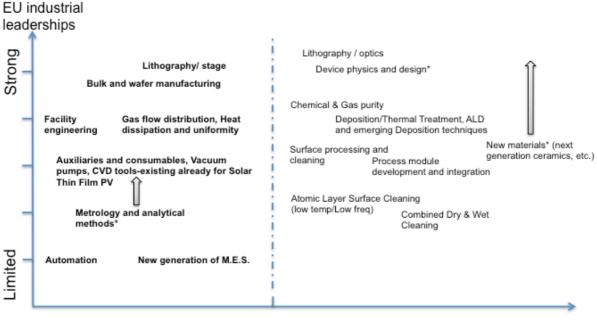

| Figure 26 – European Industrial Strength                                                 | 100  |

| Figure 27 – Market Capitalisation Of Major European SC Companies                         | 104  |

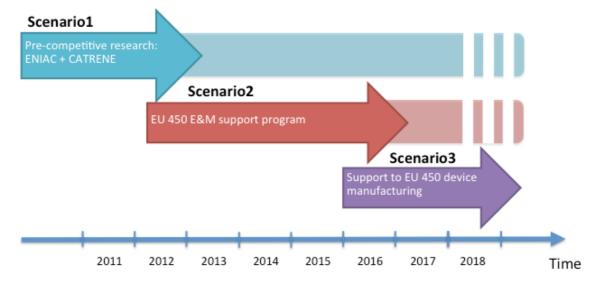

| Figure 28 – Scenarios Phased Approach                                                    | 107  |

| Figure 29 – Scenario 1 Impact Assessment                                                 | 110  |

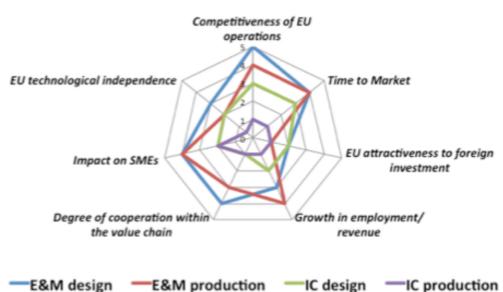

| Figure 30 – Scenario 2 (Option 1) Impact Assessment                                      | 114  |

| Figure 31 – Scenario 2 (Option 2) Impact Assessment                                      | 115  |

| Figure 32 – Scenario 3 (Option 1) Impact Assessment                                      | 120  |

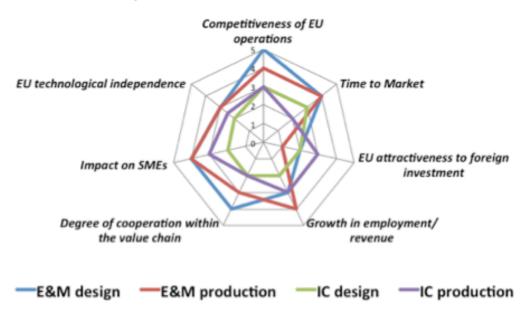

| Figure 33 – Scenario 3 (Option 2) Impact Assessment                                      | 121  |

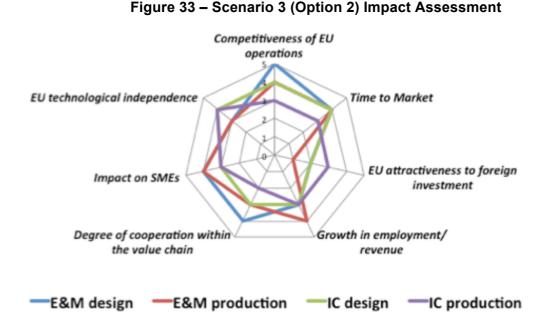

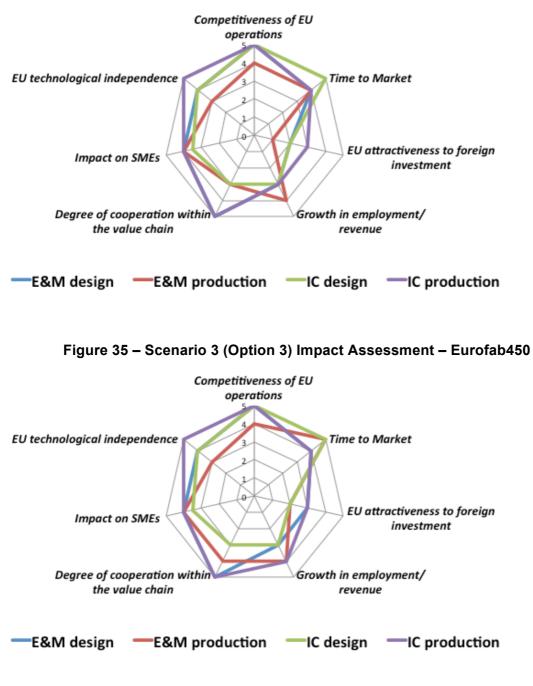

| Figure 34 – Scenario 3 (Option 3) Impact Assessment – MM fab      | 122 |

|-------------------------------------------------------------------|-----|

| Figure 35 – Scenario 3 (Option 3) Impact Assessment – Eurofab450  | 122 |

| Figure 36 – Cost Of 300mm vs. 450mm MtM & MM Fabs                 | 123 |

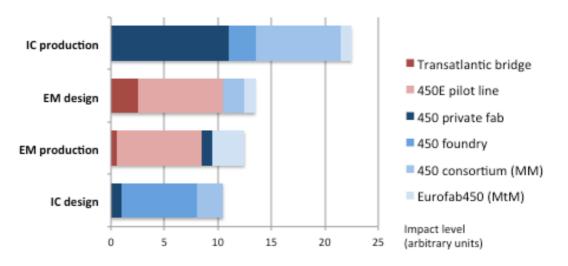

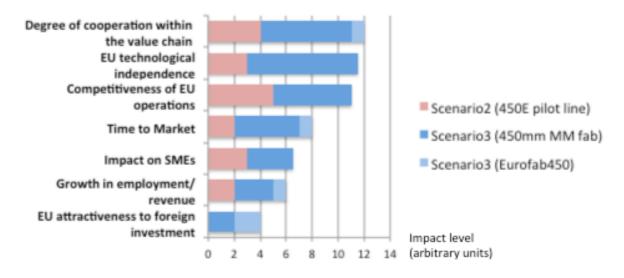

| Figure 37 – Cumulative Impact Of Scenarios (Per Type Of Activity) | 124 |

| Figure 38 – Cumulative impact Of Scenarios (Per Type Of Impact)   | 125 |

This study was assigned in December 2010 by the European Commission – DG Information Society and Media (DG INFSO) – Directorate Components & Systems (Dir G) – Unit Nanoelectronics (G1), to DECISION in partnership with Future Horizons.

It has been conducted from January 2011 to February 2012 by the following study team:

#### DECISION:

Future Horizons:

- Didier Coulon: General Manager (coordinator of the study)

- Mike Bryant: Chief Technical Officer

Malcolm Penn: Chief Executive Officer

- Sebastien Rospide: Senior Consultant (project manager)

supported by two independent industrial experts:

- Laurent Bosson

- Guy Dubois

For further information, please contact: Willy van Puymbroeck Head of Unit G1 – Nanoelectronics (DG INFSO) willy.vanpuymbroeck@ec.europa.eu +32 (0)2 296 81 38

# 1. Executive Summary

#### European semiconductor industry at a crossroads

Europe will lose advanced and competitive semiconductor (hereafter SC) manufacturing infrastructure without a European long-term industrial vision guiding and enabling the coordination of all stakeholders.

Semiconductors is a strategically important industry, providing the knowledge and technologies that generate some 10 percent of global GDP. Its high leverage on innovation cycles and wealth creation makes it one of, if not 'the' most important Key Enabling Technologies for Europe and an essential pillar of any European industrial policy.

Wafer scale-ups always bring disruptions and dislocations in the SC industry. Among the most noteworthy are increased industrial consolidation and concentration and the setting of new competitive standards and rules defined by those driving the wafer transition.

The next scale-up from 300mm to 450mm wafer diameter processing is now a certainty and 450mm fabs will be in full production before the end of the decade.

It will very likely be the final wafer scale up for the industry and will define the geographical locations of the next (and perhaps final) ten to fifteen most advanced semiconductor production areas worldwide.

Europe was at the leading edge during the 200mm to 300mm transition with the 1999 Siemens-Motorola joint venture R&D fab in Dresden the location of the first 300mm fab in the world but failed to capitalize on this strength due to continuous lack of investment especially over the last decade. It is now at a crossroads, with only three 300mm fabs and a steady decline in indigenous manufacturing activities.

From a semiconductor supplier perspective, the 450mm transition is promoted by market leaders focused on advanced node manufacturing (More Moore – MM). There is currently no commitment from European IDMs to 450mm with only one firm (STMicroelectronics) even incorporating 450mm into its long-term strategic plan. Indigenous suppliers have indeed leaderships in advanced products based on more mature technologies (More than Moore – MtM) that will continue to be manufactured on primarily 150mm and 200mm for some time to come.

But the fact remains that the transition to 450 mm will impact all levels of the European SC supply chain, from SC fabs suppliers (facilities, equipment & material suppliers) to chip manufacturers and designers, albeit with different timescales and to different degrees, depending on companies activities and portfolios. But nonetheless, all will be impacted.

Not having a 450mm production infrastructure in Europe will thus mean abdicating production of advanced SC technologies, which will sooner or later (10 years) threaten the competitiveness of the current European SC manufacturing base, including technology development and device design.

Note: investing in additional 300 mm fabs in Europe – when spare 300 mm capacity will be available in Asia – following the 450mm production ramp-up will not make economic sense for Europe.

#### Towards an integrated European 450mm strategy

The transition to 450mm will be more cost efficient than past transitions due to the increased industrial collaboration organised in Albany, NY within the Global 450 Consortium (G450C). Although the collaboration is currently US-led, Europe should play a role in this early development phase as it did in the past. It has key strengths and capabilities to put forward in equipment & material supply, as well as R&D and technology development activities.

Whatever the degree of coordination, the size of investment will nonetheless remain very significant, with total cost of industry transition estimated between US\$25 billion and US\$40 billion from 2012 up to the time when the early adopters will open their first 450mm volume fab (as early as 2018). 450mm equipment and material development and qualification will concentrate the largest investment between US\$15 billion and US\$20 billion. The cost of the 450mm transition will come in addition to existing investment in 300mm technology development and thus translate into a significant increase in funding requirement.

In this context, national 450mm strategies do not make sense and a European 450mm 'master plan' is the only sensible scale. It should be based on both a strong industrial commitment and a coordinated position of public authorities (PAs) that are the necessary conditions to leverage the required funding, avoid duplication and concentrate the funding where needed.

A European 450mm master plan should also coordinate with existing initiatives (G450C) and be open to international participation. The acknowledged European leadership in SC R&D activities should be leveraged to reach a critical mass and gain international dimension. Coordination among European R&D institutes on 450mm is critical.

The different exposure to the 450mm transition across the European supply chain calls for a phased approach corresponding to individual players' needs and agendas. Three scenarios are explored in this Report, together with their cost and associated impact for Europe:

- Scenario 1 corresponds to the 'Business as Usual' scenario whereby 450mm R&D would be supported through current cooperative programmes and budget that are currently almost exclusively focused on 300mm. Such a scenario would lead to a continuous decline in SC production activities in Europe and a progressive shift of the equipment & material industry outside Europe.

- Scenario 2 corresponds to a dedicated European master plan to support equipment and material suppliers in the transition to 450mm platforms. To maximize impact and benefits for the industry, a shared programme coordinating the leading European R&D institutes activities could be envisaged to secure the equipment & material industry in Europe, consolidate and even create new leaderships (450E pilot line).

- □ Scenario 3 finally corresponds to a process of setting up 450mm volume production in Europe with different, non-exclusive, approaches depending on fab ownerships and

technology targets. This includes the concept of a 450mm joint-fab model in Europe between IDMs (Eurofab450) in true partnership with equipment & material suppliers, initially targeting MtM products but providing a European bridge to MM technologies in due time.

#### Conclusions

Europe will lose advanced and competitive SC manufacturing infrastructure without a European long-term industrial vision guiding and enabling the coordination of all stakeholders. Such a long-term vision shall not oppose 300mm or 450mm but rather consider both in parallel as part of an advanced manufacturing continuum, taking into account all the stages of the SC supply chain.

Europe failed to capitalize on its strength during the 300mm transition, but 450mm could turn into a genuine opportunity to regain the position it once held in SC manufacturing by securing a complete SC supply chain and making sure that the most advanced SC technologies continue to be manufactured on European soil.

It could start in the short term with a five-year programme to urgently set up the 450E pilot line in Europe to support the transition of the European equipment & material suppliers to 450mm and coordinate with the US-led G450C initiative in Albany.

From a chip production perspective, the opportunity of a joint 450mm MtM fab (Eurofab450) between Integrated Device Manufacturers and a private 450mm MM fab should be investigated and progressed in parallel to their natural conclusion. Whatever the outcome, every effort must be expended by the European Commission and national PAs to ensure that all potential locations and especially the current most advanced manufacturing centres in Europe remain favourable places for chip companies to operate in.

High tech industries can only close competitive gaps during technological shifts. The 450mm shift is one of them and most likely the last one for the semiconductor industry: the European semiconductor industry is at a crossroads. The 450mm transition is a unique opportunity to launch a European industrial policy, building on its strengths (R&D, equipment & material, cooperative development) and an increased level of coordination to preserve the remaining manufacturing base in Europe and protect its innovation power in the future.

(This Page Intentionally Left Blank)

### 2. Overview

For several years now, 450mm wafer processing has been under discussion but apart from work on setting the standards and some prototype equipment, little had actually emerged. Indeed much discussion focused on whether the industry could actually afford to make this transition, how much it would cost and who would pay for it. The European Commission thus decided to undertake this project to determine the future, if any, of 450mm processing and the effect this would have on Europe.

As such, in December 2010, the European Commission awarded a contract to DECISION in partnership with Future Horizons to undertake a study on the activities required to support research and innovation in the field of advanced semiconductor production and measures necessary to attract investments and to support advanced research infrastructures, prototyping and early nanoelectronics manufacturing in Europe with particular emphasis on 450mm manufacturing, including:

- An assessment of the role of the European Commission and Governments of Member States and Regions for the establishment of 450mm manufacturing capabilities, including related value chain aspects, and overall their role in keeping semiconductor manufacturing and advanced nanoelectronics technologies in Europe

- An analysis of potential links between newly established 450mm manufacturing with existing semiconductor manufacturing capabilities and their likely impact on them both at the prototyping and high-volume level

Within weeks of the contract being signed, however, the issue of 'if' it would happen was settled, thanks to a strong joint-announcement made by Intel and TSMC, supported by Samsung. This changed some of the goals of the project making it an even more valid undertaking.

Key parts of the Report include:

- Identification of possible business cases that may assist Europe as a manufacturing base for advanced semiconductors and the effect this may have on existing semiconductor manufacturing in Europe

- An assessment of Europe's current position in semiconductor R&D together with a view on its future prospects

- Details on Europe's position in areas such as semiconductor technology and processes, equipment and equipment technologies, materials and semiconductor manufacturing itself

- □ The degree of public support offered worldwide, both financial and otherwise

- Other 'roadblock' issues which Europe may need to address

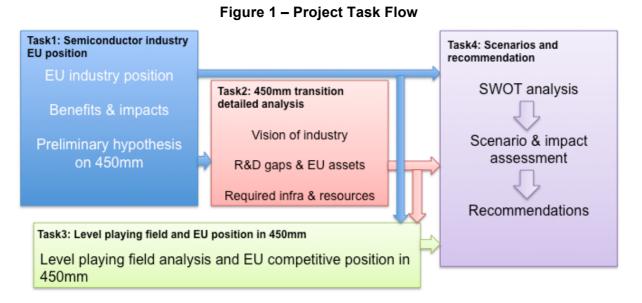

The methodology for the study was divided into four specific tasks as shown in Figure 1. Task 1 focused on the business cases for the various possibilities of what Europe's response

to the Intel and TSMC announcements could be. It provided a framework for Task 2, during which a wide range of senior industry executives were interviewed using questions generated by Task 1. Task 3 analysed the 450mm market and funding in much greater detail, whilst Task 4 brings all the results together for the final Report.

Source: DECISION/Future Horizons

The questions used during the consultation process are provided in Appendix 2. The intention of this list was to ensure that interviews covered all the important topics whilst still allowing those being interviewed to add any information they deemed important to the study.

In addition to Task 2 consultations, close links with the industry have been maintained during the study development and a Focus Group was created with the following companies involved:

Aixtron

IMEC

ASML

BOSCH

• Fraunhofer

· GlobalFoundries

ASMI

- Infineon

- - Leti

- Lfoundry

Intel

- M&W

- IDC NXP

- Two meetings of the study's Focus Group were organized in Paris in March and September 2011 to assist the study team at two critical stages of this assignment (validation of stakeholders' interview guide + validation of key findings and scenarios).

- RECIF

- Samsung

- Siltronic

- Soitec

- STMicroelectronics

- TITSMC

Finally, a Steering Group composed of key representatives from EEMI450, INTEL, SEMI Europe and STMicroelectronics was also created with four meetings held with the study team to validate the interim results and provide guidance for the remaining steps.

The information presented in this Report has been derived from Future Horizons' and DECISION's interviews with members of the semiconductor industry worldwide and with the representatives of PAs throughout Europe, together with their combined extensive database and experience in the semiconductor and related industries. The opinions expressed in this Report are those currently held by the authors and may not represent the European Commission's official position. They are subject to future change.

Figure 2 provides the list of companies and organizations directly interviewed within the scope of this assignment.

| IC manufacturers | E&M suppliers | Fabless               | Others              |

|------------------|---------------|-----------------------|---------------------|

| Elpida           | AIXTRON       | Altera                | Covalent Technology |

| Global Foundries | AMAT          | ARM                   | Hitachi Chemicals   |

| Infineon         | ASMI          | Nvidia                | KET                 |

| INTEL            | ASML          | Qualcomm              |                     |

| Lfoundry         | EVG           |                       | Programmes          |

| NXP              | FEEI          | Facility engineering  | CATRENE             |

| Renesas          | LAM           | IDC                   | ENIAC               |

| STM              | MAPPER        | M&W                   |                     |

| Toshiba          | RECIF         |                       | PA's                |

| TSMC             | SILTRONIC     | Application end users | Austria             |

|                  | SOITEC        | Airbus                | Belgium             |

| R&D labs         | TEL           | BOSCH                 | France              |

| Fraunhofer IISB  |               | Nokia                 | Germany             |

| Imec             |               | Siemens               | Ireland             |

| Leti             |               |                       | Netherland          |

Figure 2 – Project Interviews

(This Page Intentionally Left Blank)

# 3. Introduction

At the time of commissioning this Report, the future development of 450mm wafer processing was unclear. Although the standards for the wafer itself and its handling were being prepared, there was a continuing argument that the expense of developing and rolling out the technology could possibly exceed the benefits to be gained from manufacturing at this larger wafer size. Some equipment makers were even still arguing that they had not fully recovered the development cost for the past wafer scale up, from 200mm to 300mm.

As was the case at 300mm, it was clear from the outset that the expense of developing 450mm would require an element of state support, even if this investment would pay for itself in the long-term. Such transitions are also a huge drain on the infrastructure and there is thus the added risk that the short-term redirection of resources would damage the industry in other ways. For example, it has been argued that support for 450mm would divert attention and resources from the more efficient manufacturing processes being developed at the 300mm node, as well as impacting on the MtM approach many companies were adopting.

Overall it would be fair to say that there was still a lot of industry scepticism, with some organisations even wishing that this particular genie would stay locked in its bottle. By March 2011, however, the climate had changed significantly with this particular wish sidelined by Intel and TSMC's near simultaneous announcements that they intended to roll out 450mm wafer technology in their latest fab plants as soon as it was possible.

Of course these are two of the most dominant semiconductor companies in the world, and the ones who can better afford the costs of the transition, leading to comments from some parties that this was simply an attempt by these firms to cement their dominance of the crucial microprocessor, logic and potentially memory industries when, as expected, Samsung committed as well.

This may well be true but it is by no means a certainty; history has shown that leadership positions in the semiconductor industry can often be transitory whereby just one mistake can consign a company to steady decline. It will take a decade to determine whether this transition will be the correct choice for them but in the meantime the rest of the industry will have to respond in the best way it can.

As with previous wafer size changes, the transition to 450mm wafer processing cannot be done overnight, indeed some of the earlier timescales looked highly optimistic, but the intent is now clear and this new wafer size will be introduced. There is also now an increasing consensus on its timing and roll out strategy.

When the project started, we were aware of similar discussions taking place between government and industry in Japan and the US, and expected that Korea and Taiwan would also be having such discussions.

One hypothesis at the beginning of the project was that Europe simply could not afford to directly respond to this transition given it no longer had indigenous semiconductor IDMs demonstrating leadership positions at the most advanced nodes of the technology ladder and, in any case, these companies had moved some of their wafer manufacturing to the Far East whilst relying on foundries for their advanced IC processes.

It was therefore suggested that 450mm technology would simply hasten the divergence of these companies into more specialist areas, such as MtM, at least in the short to medium-term. Not requiring the latest technology today offered Europe the possibility to effectively sidestep the issue for now and instead use its resources to focus on alternative technologies in an attempt to add value to their existing fabs within Europe and elsewhere.

The converse argument, and second option considered, was that Europe had a very successful R&D, materials and production equipment industry, many of whom, for example IMEC and ASML, had globally dominant positions and extensive key IP portfolios in the most advanced processing technologies whilst others had key specialities. These European players were at the forefront of enabling this transition and for them, not just embracing but taking a leading role in the 450mm transition was an absolute priority, regardless of what Europe's indigenous semiconductor IDMs decided to do.

Also to be considered were the needs of Europe's fabless community that, although smaller in size to their mainly US peers, were also highly dependent on advanced semiconductor technologies and as such were currently forced to go to the large Asian-foundries to satisfy their needs. This raised the possibility that Europe could offer direct support to a foreignowned semiconductor foundry or IDM to encourage them to set up a 450mm wafer fab in Europe.

A third and final option considered was whether semiconductors were still an area that Europe could succeed in or whether it should focus its support into alternative technology areas. Certainly there were many in other fields who strongly argue this case. It would however have been in contradiction to Europe's current position and policy on the strategic importance of semiconductors and their role as one of only six designated Key Enabling Technologies (KETs). Such a decision would therefore have serious long-term ramifications for Europe's overall competitive global position.

Given the wide divergence of these three current options, each of which have many individual company, government and research organisation supporters, all of the options were investigated and evaluated impartially, based on the merits of the arguments and global industry trends.

Key to the final recommendations of our analysis was what would be best for Europe, even though this was almost bound to contradict the strategic policies and preferences of some individual European governments and organisations. Given the wide divergence of views and opinions initially encountered, we were originally concerned that it would be unlikely everyone would be satisfied and happy with the outcome of this study.

Thankfully, however, as the project progressed and the results openly debated at the various company, Steering and Focus Group discussions, we were able to keep the debate focused on the issues rather than individual company or national preferences.

Whilst we do still expect to see individual company, and even national, nuances of interpretation, we are highly confident that this Report represents a fair and honest reflection of today's 450mm transition reality.

# 4. State-Of-The-Art SC Manufacturing In Europe

#### 4.1. Introduction

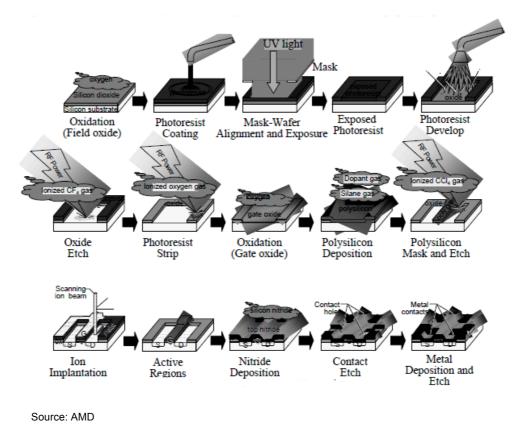

Processing a semiconductor wafer of any size is a complex task. The very simplified diagram below shows some of the major processes, though in fact many of these are themselves quite complex and repeated several times. For example, at 28nm there can be up to 12 layers of metal so the final task "Metal deposition and etch" may involve 60-80 process steps alone. In all, the wafer will undergo between 500 to 600 sequential operations from start to finish, each of which must be strictly controlled and managed.

Figure 3 – Simplified Wafer Fabrication Process

Each process step requires different equipment and each tends to have just one or two suppliers. Probably the key step to the final performance of the IC is the lithography process where a photo-resist coating on the wafer is exposed to an image from a photo-mask. What was once a fairly simple process is now vastly more complex for the simple reason that the wavelengths of the ultraviolet light used to expose the photo-resist are now about an order of magnitude larger than the details on the wafer needing to be etched. Numerous techniques

are used to enhance the accuracy and detail on the resist, the impact of and further details on this will be discussed later.

### 4.2. IC Manufacturing In Europe

During the 1990s, Europe saw a growth in new fabs but, despite having driven the development of 300mm wafers in an attempt to stop the flow of manufacturing to the Far East, Europe fell significantly behind in semiconductor production during the last decade. Old fabs closed with few new ones opening to replace them. Whereas Europe accounted for approximately 11 percent of world chip production in 2000, its production share has decreased to just under 5 percent in 2011.

With hindsight, the biggest loss during this period was the closing of Qimonda in February 2009 when it filed for bankruptcy, just 1-2 quarters before the memory market staged a dramatic recovery. Their well-equipped 300mm fab was dismantled with some of the equipment auctioned off at well below market value; this now forming the basis of Texas Instruments' transfer of analogue IC production to 300mm wafers in a US fab. This loss however may now be partially recovered following Infineon's decision to purchase the Qimonda cleanrooms and remaining assets 'for 65nm analogue/power IC production', almost certainly as a competitive response to TI's 300mm analogue fab decision.

The other negative event was the failure to facilitate and equip STMicroelectronics' Catania 300mm fab shell which is now been used by 3Sun (a joint venture between Sharp, ENEL and STMicroelectronics) to make PV wafers instead.

The largest fabs currently operating in Europe are those of Intel (Ireland) and GlobalFoundries (Germany), both of which are being significantly upgraded to handle the latest 300mm technologies thereby assuring some high-volume advanced IC manufacture remains in Europe.

At the low-volume end of the scale, STMicroelectronics' plant in Crolles utilises 200mm and 300mm wafers and works down to the 28nm node on the 300mm line. However its capacity is limited to around 17k wafer starts per month versus the 80k per month planned for the GlobalFoundries Dresden complex once the expansion is completed. Crolles is often referred to as a lab-fab where (a) new technologies are developed (b) new products are first run before transfer to foundries and (c) low run-rate, high-value specialist ICs are made, such as STMicroelectronics' huge die area networking ICs.

Finally, at the advanced research level, IMEC has a 300mm clean room that is equipped to the very highest standards and is arguably the best R&D centre in the world. It is already capable of producing 8nm structures, 5nm by hand if necessary, on a par with the world's best, namely IBM, Intel and Toshiba. Leti is primarily focused on advanced SOI processing, resists and mask-less lithography and the combination of Leti's process capability and Crolles 300mm line provides them with a quasi-300mm R&D capability. These advanced research infrastructures are used both for the development of new processes and for testing and working on new equipment from their commercial partners, especially at IMEC.

Extending Europe's 'high-tech borders' to Israel, both the Intel and Micron (ex-Numonyx) fabs there are advanced manufacturing lines but there are now no other meaningful state-of-the-art fabs within Europe capable of processing advanced technology nodes; most others

are 200mm wafer size or less and, as far as we are aware, it seems reasonable to surmise that the existing European manufacturers are not currently considering building new 300mm fabs in Europe.

#### 4.3. European Companies Manufacturing Elsewhere

This dearth of European-based manufacturing plants might be reasonable if European companies had sizeable state-of-the-art fabs located elsewhere, e.g. for reasons of cost. However what plants the European companies do have are far below the state-of-the-art from both a wafer size and technology node perspective. Infineon has a plant in Malaysia making 350nm power devices on 200mm wafers, NXP has nothing and STMicroelectronics produces power devices on 150mm in Singapore, albeit at an impressive over half a million wafers per month level, which does go to show Europe's chip firms do have the expertise to run high-volume wafer fab plants were it mindful to do so.

### 4.4. The 'Fab-Lite' Alternative

European semiconductor companies have instead all taken the approach of using foundry services from TSMC and others in a strategy labelled 'fab-lite'. Squeezed by a presumption of 'ever-declining' ASPs (no longer true), a more mature single digit market growth in value terms (a questionable extrapolation), and the success of fabless competitors like Broadcom, MediaTek and Qualcomm, many IDMs came to the conclusion that advanced in-house wafer production was both too expensive and unnecessary, with no strategic value or commercial market benefit. This gave birth to the fab-lite business model which was enthusiastically adopted by IDMs everywhere in the last decade to the delight of the financial community as a way of reducing capital requirement whilst still satisfying both the needs of their customers and investors at seemingly zero risk to the supply chain.

Numerous arguments have been provided in support of this move, such as: wafer fabrication has become a service operation, a simple make-buy decision best left to outsourcing; foundries were fundamentally more efficient than IDMs in ramping up production and loading their lines meaning they can make wafers much cheaper than in-house production, especially in advanced technologies; the semiconductor industry has been outsourcing backend manufacturing for decades without any problem; and fabless companies had constantly out-performed IDM's growth with no competitive disadvantage by not having a fab.

Contrasting this with the IDM having to own and operate a fab, thereby tying up cash and management resources, 'fab-lite' appeared to both solve the inherent fab ownership operational (loading and constant investment need) problems and level the playing field with the IDM's fabless competitors. But the justification and implementation has since become muddled, with terms such as 'asset-lite' or 'asset-smart' introduced, implying these are subtly different and implicitly better than 'fab-lite', casting doubt over the robustness of this business model. Rhetoric aside, there are really only two fundamental 'fab-lite' varieties.

The first option is to maintain a small in-house wafer fab, often known as a 'lab-fab', to prove out each process node but then outsource to a foundry the bulk of production. This is essentially the current STMicroelectronics approach and has the advantage of keeping up with technology, provided the facility is constantly upgraded for future node transitions. This appears an elegant solution were it not for the fact a small pilot fab can never be costeffective against a large volume fab, where it has been calculated that the minimum size to be within the top 20 most competitive fabs on manufacturing cost should be in the range of at least 30-35k (real) wafer starts per month. For a 450mm fab, this would be equivalent to a capacity of around 160k 200mm equivalent wafer starts per month.

Proponents of this route will thus face perpetual hostility from investors and the financial community asking why they are tying up capital in expensive assets and depleting shareholder value when the outsource supplier is clearly much cheaper. The only way around this is to look for the local government to help pay for every upgrade to the lab-fab and effectively subsidise the operating losses, and/or spreading the cost burden between several partners jointly operating the lab-fab as was the case of the ST/NXP/Freescale Crolles 2 Alliance. This does not however reduce the overall cost penalty in fact it might even increase it due to the added layers of bureaucracy so does nothing to address the overall scale lack of competitiveness.

The second option is to stop building fabs completely at a certain process node and then exclusively use a foundry for each subsequent process node. This is the route that e.g. Infineon and NXP have taken in Europe along with Fujitsu and Renesas in Japan and Freescale in the US. This is clearly a bipolar structure; IDM up to a certain node and then fabless thereafter. Unlike the first option, this strategy is process-terminal as, once you miss a wafer fab node, it will become virtually impossible to re-enter the wafer manufacturing business at a subsequent technology node without a lot of delay and money, if at all.

It also combines the worst of both worlds. For the legacy fabs it ignores the fundamental reality that today's leading edge is tomorrow's commodity meaning these fabs will slowly become more and more obsolete and harder to fill. There might be some scope for migrating these lines to some alternative niche technologies, like power devices or sensors that are not following the same technological route and address low volume and highly fragmented markets, but by there very nature (low volume – highly fragmented) these markets will only delay not arrest the decline. Eventually they too will need to be upgraded.

They will also be subject to constant threat from attack from fully-depreciated, more efficient, larger wafer size fabs with a far lower cost structure; a strategy used many times in the past by STMicroelectronics and more recently by TI in the power/analogue market. The real danger here will be once the 450mm transition gains momentum and the now-redundant 300mm lines seek new markets to address, they will inevitably move downstream with a more efficient and lower cost structure, squeezing the older fabs into ever smaller niches and volumes.

There is thus a real danger that these safe haven market niches and product specialties might simply end up being a stay of execution. With the exception of Dresden (GlobalFoundries and now Infineon via its recent acquisition of Qimonda's assets), Europe might well find itself wide open to attack on this front given its predominantly 200mm/150mm manufacturing base (see Chapter 8).

Europe's chip companies will thus be subjected to a constantly on-going closure and restructuring effort, damaging employee morale and affecting costs and productivity. Finding and keeping good operations personnel will be very difficult indeed given this business strategy is an operations career dead end.

The legacy overhead infrastructure, costs and inefficiency will also be much higher than with a truly fabless company and overall competitiveness will continue to erode. In short, restructuring from an IDM to a fabless business model will be challenging and unlikely to make the organisation more structurally competitive.

Aside from these issues, there is also the fundamentally unsound assumption that foundry wafers will always be cheap and freely available. This is the chip industry equivalent of the 'debt is freely available and cheap' corporate business model that came to such an abrupt and catastrophic halt in the 2007 financial crisis.

Just as with cheap debt, ever reducing prices (and profits) whilst simultaneously investing in new process and production technology cannot be sustained forever as they would lead to bankruptcy. Structurally prices must eventually increase; indeed they are already doing so.

Then there is the allocation and key account issues. Not everyone can be on the foundry's 'A'-list of accounts, which inevitably means losing control of time to market and time to revenue. The A-list customers will always receive priority, affording them a competitive market advantage. As processes become ever more standardised, so everyone will be channelled to use the same identical building blocks with no scope for process tweaking, this early technology access will be a potentially huge market advantage.

Finally, from a competitive market standpoint, if a firm like e.g. Nokia buys its next generation mobile phone chipsets from say Broadcom, Freescale, MediaTek, Qualcomm, ST-Ericson and TI who in turn then all source their wafers from TSMC, Nokia is effectively single sourced on TSMC. The whole livelihood and future of such OEM firms is thus dependent on a firm with whom they have no direct contractual agreements or commitments. Based on current plans, at the 32/28nm node, all of the other foundries, including GlobalFoundries, are currently too small in size or suffering yield problems to make a volume difference in the short to medium term, and this will only likely get worse as the technology road map rolls out.

The security of supply aftershock from the March 11, 2011 earthquake and tsunami in Japan temporarily refocused the spotlight on the strategic value of ICs (i.e. wafer production) and the fundamental perils of outsourcing and losing control of the supply chain but even this lesson has already been forgotten. Were such a catastrophe to ever hit Taiwan – itself on the same fault line – virtually the whole of the world's advance foundry SoC IC supply would grind to a halt, with no chance for any other factory to take up the slack.

These are the underlying long-term structural Fab-Lite issues. Future Horizons has long stated that the 'fab-smart' strategy remains the only true solution. This means continuing to build in-house state-of-the-art fabs while outsourcing a modest amount (say 5-15 percent maximum) to foundries to both smooth the supply and demand peaks and build external fab demand high enough to justify equipping the next module of in-house expansion. In this way any expansion in capacity enters production 'fully loaded' from the beginning whilst simultaneously improving response time to near-term demand fluctuation. The foundries do not like this option of course but this is the only real IDM competitive reality.

As already mentioned, partnering with a competitor(s) is of course another possible strategy – a scaled up version of STMicroelectronics, NXP and Freescale at Crolles 2 – to help defray the investment costs and provide additional fab loading, but this must be run and operated on best-practice foundry principles. It would require a fresh 'out-of-the-box-thinking'

operational management and investment approach, but we do not believe this is beyond the imagination of the chip making community were it mindful to so do.

Fabs have always been expensive but, as a percentage of revenue, they are relatively no more expensive today than they were in the 1970s. This basically means, to stay at the forefront of the business, firms need to keep up the pressure on sales, which in turn means a constant investment in new products. Failure to do so puts enormous pressure on cost reduction instead, which in turn triggers a slow downward spiral of cutting back on investment and R&D, the two cornerstones to future product development.

At the same time, the chip is still very much the heart of the product and downstream systems business; lose control of its manufacture and you will eventually lose control of not only your business but your customer's business as well. It is this that makes wafer processing so strategic in nature.

### 4.5. European Market Position

Since its peak at the end of the 1990s, when three of Europe's IDMs were in the worldwide top ten and STMicroelectronics vied for second place in the semiconductor manufacturer tables, European manufacturers have slipped inexorably downwards. Their once profitable mobile phone chipset divisions have been divested or sold off, as have the rather less profitable memory divisions, leaving them to concentrate on other so-called core competences, despite the fact that what customers – and System on Chip / System in Pacakge (SoC/SiP) devices – really need are 'one-stop shop' solutions.

STMicroelectronics still has a broad range of products and expertise but a considerable amount of this is in power, lighting control and Micro-Electro-Mechanicals (MEMs) devices, where it is the world leader, and in analogue and Microcontroller Units (MCUs), where it is near the top. None of these require the latest advanced technologies and are being successfully manufactured in Singapore, Europe and foundries. Its limited demand for mixed-signal SoCs requiring finer geometries are produced either at Crolles or its foundry partners.

Infineon has consolidated itself mainly on the Industrial and Automotive markets where it is one of the world leaders. It still has a 90nm 200mm wafer plant in Dresden, recently augmented by its recent Qimonda 300mm asset acquisition, but it is now solely reliant on foundries for its advanced logic devices.

NXP has also downsized significantly having sold off several divisions following its purchase by Private Equity. It still has staggeringly large debts and continues to be a 'restructuring work in progress'. NXP has a very long standing partnership with TSMC, who they assisted in starting up, which it uses for advanced products including a jointly owned 200mm line in Singapore (SSMC).

ST-Ericsson was formed by the consolidation of the mobile phone operations of several European companies. It is a fabless operation and we estimate that their current level of sales would fill a fab demand for around 50k 300mm wafers per month. As such, they represent the major target customer for any advanced European fab. However at this volume, which effectively fills a fab, they may be receiving very preferential terms from their current supplier(s).

Intel's mobile phone division was purchased from Infineon in 2010 and had an excellent year mainly the result of its hold on the Apple iPhone and some other key design-ins. However Intel and Apple are not always the best of friends, despite Apple changing to Intel processors in its Mac products some years ago, and the CDMA version of the iPhone4 uses a Qualcomm chipset. The success of this division depends on who has won the baseband slot in the iPhone 5 design and so it is hard to predict this group's future wafer usage.

Cambridge Silicon Radio (CSR) is the top European fabless organisation and the dominant supplier of short-range communications ICs. They are consolidating this position well with a wide range of future products essential to the wireless generation. We estimate that they currently use about 2k 300mm wafers per month which, although not fab filling, would help to load a European foundry.

There are a number of other relatively large European fabless companies, for example lcera (purchased by nVidia in May 2011) and PicoChip (purchased by MindSpeed in February 2012) but, as with Japan, Europe never really succeeded in cultivating these from the vast number of new start-ups it has spawned over the years, unlike the US and Taiwan which have both embraced this model well. This is an area that could well be improved by the presence of an advanced state-of-the-art 450mm foundry in Europe.

The research carried out as part of the Task 2 interview process, together with discussions undertaken with the Global Semiconductor Alliance (GSA), did seem to indicate, at least anecdotally, that Europe's fabless companies would benefit from the presence of a European-based 450mm fab offering foundry services. Our belief is thus that the presence of such a foundry would indeed help to develop start-up clusters across Europe, due to the easier technology access and increased share of foundry mind augmented by the considerably reduced time and cost of not having to regularly commute between Asia and Europe. We also believe that it would benefit the more integrated firms as well.

The cluster effect is discussed in more detail later but the potentially large gains in high income employment offered by new start-up companies across Europe using a European foundry is one of the major considerations that should be taken into account.

Last, but by no means least, amongst the top global European firms is ARM. It is second only to ASML in market capitalisation and profit, despite the fact that it only sells semiconductor IP. Its breadth of influence is however growing way beyond mobile devices, having now been assigned the task of developing all of the standard cell libraries for the IBM Alliance (down to at least the 11/10nm node) and have more recently started working much closer with TSMC with the implicit aim of achieving the same there. Apart from Intel with its proprietary in-house needs, this would leave ARM as the sole provider of advanced CMOS logic IC cell libraries. Thus, whilst ARM may not be directly relevant to 450mm wafers, they have now become a critical link in advanced CMOS logic design which in turn is now directly coupled to the 450mm transition.

### 4.6. Other European Manufacturing Strengths

The major suppliers of equipment are covered in later chapters of this Report; we just wish to point out here that Europe is a world leader in many aspects of supply to the semiconductor

industry, mostly due to hugely successful JESSI and follow-on MEDEA programmes together with European Commission supported fundamental research.

For example, ASML based in the Netherlands, supported by research at IMEC, is the world expert at semiconductor lithography. Although it is still uncertain how the 450mm transition will impact lithography technologies and equipment suppliers, ASML leadership position in advanced lithography processes is likely to be confirmed during this transition.

Europe is also the world leader at supplying Silicon On Insulator (SOI) wafers and, although Intel, Samsung and TSMC use bulk wafers, it is likely that GlobalFoundries will still offer these as a processing option given AMD and IBM both use SOI for some of their current devices. STMicroelectronics is also a user of SOI wafers at Crolles.

RECIF is one of the world leaders at robotic wafer handling and companies such as AIXTRON and ASMI (world leaders in ALD – Atomic Layer Deposition), Siltronic (bulk wafer manufacturing) and others also win business worldwide.

What all of these companies have found is that Asia now represent the majority of their sales and Europe only a very small portion. If this is not remedied then it is quite possible that more of their operations, including eventually R&D, could move to be nearer their customers. Should this happen, it would almost certainly undermine Europe's success in developing and building network clusters of excellence and be a great loss to Europe, both from a technology and job creation perspective.

We are thus of the opinion that it is crucially important to establish a 450mm manufacturing presence in Europe as a necessary condition for keeping and further developing such clusters in Europe.

#### 4.7. Semiconductor Manufacturing Conclusions

The situation for the European manufacture of advanced CMOS logic semiconductors is not very good. Current own-produced volumes are low (STMicroelectronics) or non-existent (Infineon and NXP) made worse by the fact that, whilst STMicroelectronics is still one of the few remaining broad range supply firms worldwide, together with Renesas and a lesser extent TI, even these companies are driving to streamline and concentrate on their perceived market strengths. This will inevitably have an effect on the type of semiconductors they produce and, if these are not at the most advanced technology nodes, there is less justification in paying for or using a state-of-the-art 450mm wafer fab.

That said, STMicroelectronics still has the need for advanced wafer production, for example for its range of Set-Top-Box and networking products, but its current run-rate means it cannot fill an economically sized 450mm plant. It is also not profitable enough to generate the cash needed to build a full-scale 450mm wafer fab.

Infineon has a similar but more focused strategy and probably less need for the most advanced geometries. Its requirements are more for devices with on-board communication and volatile/non-volatile memory to produce truly single chip systems for its target market. We believe such devices are just moving to the 65nm node so the inherent lag in these products makes access to a state-of-the-art 450mm fab plant less important. However they will require access to such a plant once it is amortised and behind the state-of-the-art node.

Unfortunately at the moment the use of Far Eastern foundries does appear the best way to achieve this, although GlobalFoundries may present an alternative in the future.

NXP does have some product lines that require state-of-the-art nodes but their long-standing relationship with TSMC might be a huge barrier to entry for a new European-based fab, given that it might not, at first glance, seem to be in NXP's best interested to risk potentially damaging this long history of co-operation. However, looking at it from a purely financial perspective, whereas NXP needs TSMC, it could be argued that TSMC does not necessarily need NXP, so the presence of a 450mm foundry in Europe might also be to NXP's strategic advantage.

For the time-being, ST-Ericsson still has the potential to achieve a successful re-organisation and remain one of the top-tier players in the mobile chipset market, together with Qualcomm, Broadcom and MediaTek, with a few second-tier players left to exploit some niche areas. The mobile chipset market remains huge and in the future, with the move to 4G, Qualcomm may have less of a stranglehold upon it. Provided ST-Ericsson can win key design-ins then they will continue to need huge numbers of wafers at the most advanced technologies but it has to be said its time is running out. It is also hugely loss-making which severely limits its options.

Beyond these, there are a number of smaller fabless companies who could also use a European 450mm fab if it offered foundry services and was fitted to economically process small to medium-volume orders. Such availability could also assist in unlocking investment capital for other start-ups who are currently not winning investment due to issues such as tight lead-edge wafer capacity, meaning they will never have early access to state-of-the-art advanced CMOS processes. This would need to be offered and staffed accordingly in a way that was cost-effective for the foundry otherwise it would negatively impact the overall 450mm project but, with a fresh open box approach, as with the co-owned option, we do not see this as a major barrier to overcome. Access could be readily co-ordinated and sold via existing European programmes such as Europractice.

Taking all of these factors into account, it would seem reasonable to conclude that there was sufficient need and market demand to support at least one high-volume, state-of-the-art 450mm wafer fab in Europe provided it offers foundry services both to Europe's fabless community and the indigenous IDMs. It can only be justified however if sufficient charter key European companies were committed to its success. Once established we believe such a fab would also prove attractive to the leading global fabless (Broadcom, nVidea and Qualcomm etc) and fab-lite (Freescale and Renesas etc) firms, thereby enhancing its cost structure and economic feasibility.

Looking at the broader agenda, there is also the possibility to persuade one of the top three 450mm pioneers (Intel, Samsung and TSMC) to set up a 450mm fab in Europe, capitalising on the rich European 450mm advanced R&D and cluster infrastructure. This might also open the door for GlobalFoundries to participate earlier than they might otherwise have been able to, and every effort must be expended to ensure that all potential locations, especially Leixlip and Dresden – Europe's two most advanced manufacturing centres – remain favourable places for chip companies to operate in.

Given Europe's commitment to developing and keeping advanced manufacturing in Europe, whatever strategy is eventually adopted, it will need to ensure that Europe remains a

competitive place for its equipment and materials manufacturers and advanced research institutes to operate in, even if the bulk of their business resides in the Far East.

In addition to this opportunity, we further believe that there is a parallel opportunity for a European-based 450mm wafer fab focused on more mature technology node processing. Whilst this may at first glance sound like a nonsensical idea, especially as 450mm and advance-state-of-the-art processing have become de-facto synonymous, it would actually help both de-risk the 450mm transition – by providing a platform to run proven technologies for a much longer period of time envisaged by the current state-of-the-art 450mm roll out on – and provide an advanced, lower-cost manufacturing platform for Europe's MtM-based technologies.

The fab would need to be designed and built 'future-proof', in order to avoid building a blind alley, which in essence means designing it to be a high-volume state-of-the-art MM fab but initially only equipping it with the equipment and facilities needed for lower technology node MtM production. For example, this would mean making sure that the fab can accommodate the advanced EUV and immersion lithography needed for sub-65nm production, but housed in an adjoining building Annex so that this part of the facility does not need to be constructed at the start of the project.

The lower processing complexity would also mean less equipment was required for the main wafer fab but this too would be built to accommodate complexity expansion over time. On starting up therefore, the fab would be equipped with 450mm tools required to process 65nm and higher structures. This toolset would then be gradually updated to accommodate more advanced process and state-of-the-art nodes in due times.

We further believe that there is collectively enough production volume to fill such a largevolume fab, given the majority of Europe's current production at these nodes is in older, 150nm and 200mm fabs, all of which need expanding and/or upgrading within the next five years, i.e. the timescale of this project.

Consolidating this into a single 450mm fab would bring huge benefits in production efficiency, technology capability and die cost reduction. The yields, scale and efficiency of the resultant production will be significantly better that those for its competitors, even if on a fully depreciated 300mm line, giving Europe's MtM chip firms a huge market advantage...a unique European win-win scenario.

There would also be benefits to the equipment industry and Europe's research facilities by helping to engineer solutions to the 450mm-wafer size related problems, using even more well-established nodes over a much longer period of time and allowing MtM technologies to be developed on a 450mm platform much earlier than would otherwise be possible.

This option is discussed in more detail later on in the Report (see Chapter 17).

# 5. The 450mm Bifurcation

The purpose of the following chapters is to provide the reader with an overview of the 450mm transition process and its anticipated impact on the SC supply chain. A timescale for the 450mm transition is also provided based on early adopters' announcements and industry's readiness level.

### 5.1. 450mm Rollout Scenario

There are still some dissenting opinions as to whether the semiconductor process node road map and the transition to 450mm wafers are independent topics or if the two will need to become intrinsically linked. This is complicated by the fact that the technology roadmap, from today's 32/28nm advanced production node to the 11/10nm structures we can expect to see in early production around 2015, are littered with process dislocations, both in the structure of the transistors and the means to pattern and build them.

One of the lessons to be learnt from the 300mm conversion was that the two issues were initially isolated, meaning that the conversion node became a moving target, starting off at 250nm, ultimately ending up as 90nm, causing a raft of false starts, overlapping and redundant equipment development costs. It is this 'wasted' R&D spend that bruised the equipment industry so badly, hence their reluctance to readily embrace the 450mm transition.

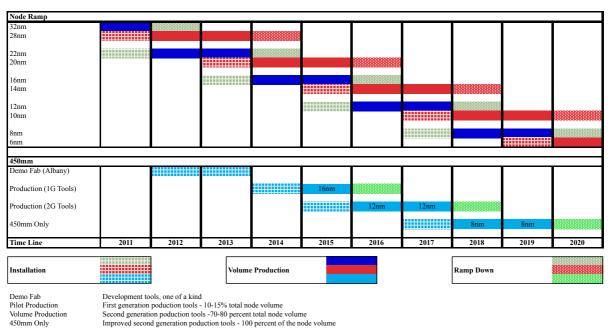

Whatever the conclusion of this debate, consultations across the SC industry confirmed that the 450mm rollout must and will be better coordinated across the supply chain as already shown by the G450 Consortium in Albany formalized and publicly announced on September 27<sup>th</sup> 2011. In our opinion three things are becoming clear:

- □ The first pilot production 450mm wafers will be on a proven (n-1) high-volume production process and mature chip design in order to run-in, match and then (hopefully) exceed all of the measurable 300mm process performance characteristics

- Once process and platform stability has been achieved (one year?), the process technology will flip to the then current leading edge node resulting in parallel chip production on 300mm and 450mm lines, during which time 450mm development will be focused on yield, cost improvement and production volume ramp-up

- Once cost parity has been achieved (or in sight), production will immediately flip to 450mm only with 300mm phasing over to less demanding application areas, such as chip sets, controllers and more mature SoC ICs

### 5.2. SC Industry At A Cross-Roads

At the time of introduction, and for the first year of operation, 300mm fabs will be operating at a more advanced node than early 450mm fabs and 450mm produced die will likely carry a cost penalty compared to their 300mm fabbed counterparts.

However, once parity has been reached, the cost benefits will start to gain traction and, for those firms on a 450mm platform from that point on all future advanced-node development across their entire product range will be solely on the 450mm platform. Existing 300mm production capacity at that node will be either progressively phased out and the equipment sold on, or turned to other less demanding areas, for example to cost reduce 200mm-based products.

For these firms 300mm capacity expansion will be focused on process improvements limited to implementing best practice and/or improved processing techniques stolen from their 450mm experience wherever this is practical, as with e.g. CMP at the 200mm size. This will leave the equipment industry with limited R&D resources and dwindling long-term 300mm demand to focus solely on 450mm. It only takes one firm to drop 300mm support at the state-of-the-art for it to be impossible for a complete state-of-the-art 300mm fab to be built.

This bifurcating moment for the semiconductor industry has been confirmed during Task 2 interviews indicating that once 450mm enters full-scale production, further 300mm node development will cease for equipment suppliers due to the following reasons:

- Equipment industry will have limited resources and concentrate on the largest share of the market providing the largest Return on Investment. At the time of the transition, between 60-75 percent of the Capital Expenses (Cap Ex) dollars will be driven 450mm demand from the world's chip market gorillas, with the residual, and declining, Cap Ex coming from the rest of the industry

- 450mm platforms will be more competitive from a chip manufacturer's cost perspective and common platform / body 'proposal' capable of processing both 300mm and 450mm wafers will not be economically viable for a vast majority of equipment suppliers (about the same cost but only half the throughput)

Following the wafer scale-up, future node development will rapidly occur only on the 450mm platform, although there will of course still be further developments on larger nodes on the 300mm platform under the MtM concept.

Faced with competitive pressure from their 450mm-based competitors, the only course of action for 300mm fabs will be to (a) somehow address their upgrade path to 450mm, either by becoming 100 percent fabless at these process nodes (by then the so-called 'fab-lite' model will not be an option); (b) merge and/or form production joint ventures; (c) continue to face slow death by competitive market strangulation; or (d) exit these markets and move into other niches and/or specialty product, in much the same way as Europe's chip firms did at the 300mm/65nm node.

This latter group of firms will thus be joining what will be an increasingly overcrowded market as more and more competitors are forced into market niches and speciality products both of which are, by definition, relatively small and diverse. To make matters worse, whilst it may well be the case that their advanced technology base is still at least 1-2 nodes behind the leading edge, meaning they will likely have at least 2-3 nodes 'in the bag' yet to embrace, within 5-6 years from transition they will find that the only place they can get their base technology from will be a 450mm platform. They too will de facto become fabless, other than for legacy products.

In the near-term the issue is somewhat irrelevant; the two wafer sizes will be co-developed, meaning all next generation 300mm equipment will be developed with 450mm features and requirements in mind. The first generation 450mm fab production (pilot) line equipment will be process robust and production fab ready, as opposed to the 'throw-away' early test wafer and demo tools, albeit not yet optimised for performance and throughput. These tools will be capable of operating at the then most advanced node, exactly in synch with their 300mm counterparts. They will not however start production at this node.

### 5.3. Early 450mm Entrants & Products

The first 300mm pilot lines took almost a year to achieve comparable yields with 200mm wafers and there is no reason to believe things will be any different with 450mm. Thus the early 450mm adopters will have to manage this changeover period when finished die from a 450mm fab will actually cost more than those from a 300mm fab.

Once the pilot line is at acceptable yields, it will then be necessary to equip the rest of the fab to achieve full capacity. Even assuming the necessary processing equipment is available, possibly due to an advance ordering mechanism similar to the manner civil aircraft are ordered, it will still take a further two years for the early volumes fab to reach full production.

#### 5.3.1. Intel

Intel is the prime driver in the move to 450mm wafer processing and they have stated their intent to run in the first line on a proven process/IC design combination at the 15nm node before moving to 11nm once everything is proven capable of operating at this node properly. Although any new line is debugged first using test chips, being already in mass manufacture of the same part on their 300mm lines provides a perfect reference to allow them to optimise the new equipment and process flow.